CPLD可编程数字信号发生器实验

一、实验目的

1.熟悉各种时钟信号的特点及波形

2.熟悉各种数字信号的特点及波形

二、实验电路的工作原理

(一)、CPLD可编程模块二电路的功能及电路组成

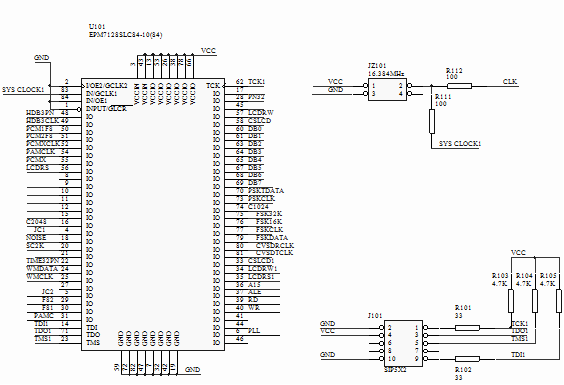

图1-1是CPLD可编程模块的电路图。

CPLD可编程模块(芯片位号:U101)用来产生实验系统所需要的各种时钟信号和数字信号。它由CPLD可编程器件ALTERA公司的EPM7128(或者是Xilinx公司的XC95108)、下载接口电路(J101)和一块晶振(JZ101)组成。晶振用来产生16.384MHz系统内的主时钟。本实验要求参加实验者了解这些信号的产生方法、工作原理以及测量方法,才可通过CPLD可编程器件的二次开发(本实验箱提供专门的开发模块)生成这些信号,理论联系实践,提高实际操作能力。

(二)、各种信号的功用及波形

1.83脚输入16.384MHz主时钟,方波。由晶振JZ101产生的16.384MHz时钟,经电阻R111,从83脚送入U101进行整形,然后分频、产生各种信号输出。

2.16脚,输出2.048MHz时钟,方波。

3.74脚,输出1.024MHz时钟,方波。

4.49脚,输出64KHz时钟,方波。

5.75脚,输出32KHz时钟,方波。

6.76脚,输出16KHz时钟,方波。

7. 48脚,输出32KHz伪随机码。

8. 79脚,输出2KHz伪随机码。

9. 50脚,输出8KHz的窄脉冲同步信号,供PCM(一)编码模块用(时隙可变)。

10.51脚,输出8KHz的窄脉冲同步信号,供PCM(二)编码模块用(时隙可变)。

8KHz的窄脉冲同步信号,可通过编程来改变它们的时序和脉冲宽度,学生可通过薄膜键盘选择,供PCM(一)模块、PCM(二)模块使用

电原理示意图见如图1-1所示,由CPLD芯片U101、下载接口电路J101、一块晶振JZ101及外围一些电容电阻组成(有兴趣的同学,可以到网上搜索相关原器件的详细资料)。

注:本实验平台中所有数字信号都是由同一个信号源JZ101分频产生,所以频率相同或者频率成倍数关系的数字信号,都有相对固定的相位关系。

图1-1 CPLD可编程模块电路图

三、实验内容

1.熟悉CPLD可编程数字信号发生器各测量点信号波形。

2.查阅CPLD可编程技术的相关资料,了解这些信号产生的方法。

四、实验步骤

1.打开电源总开关,电源指示灯亮,系统开始工作。

2.用示波器测出下面所列各测量点波形,并对每一测量点的波形加以分析。GND为接地点,测量各点波形时示波器探头的地线夹子应先接地。

各测量点波形如图1-2所示,具体说明如下:

以下信号均由CPLD可编程器件EPM7128芯片编程产生并送往各测量点。

TP301:1024KHz的时钟信号,作为PSK调制模块中产生载频信号用。

TP901:32KHz的时钟信号,作为FSK调制模块中产生载频信号用。

TP602:方波信号,作为抽样定理模块中抽样时钟用。可由薄膜键盘选择“抽样定理模块”中不同的抽样时钟信号(默认为2KHz方波)。

TP503: 8KHz的窄脉冲同步信号,可通过薄膜键盘选择不同时隙。

测量时将示波器通道1的探头放在TP509上(固定0时隙和脉冲宽度),将通道2的探头放在TP503上,调整通道1为触发通道,通过薄膜键盘选择“PCM编译码模块”中不同选项,对比两路波形可以看到8KHz的窄脉冲同步信号不同的时序关系和脉冲宽度。

TP110: 15位的伪随机序列码,码元速率为32Kb/S,码型为111100010011010,可对比TP901的32KHz的时钟信号读出它的码型序列。该波形用来输岀到PSK调制等模块单元,作为数字基带信号。

TP905:K901开关1-2连,15位的伪随机序列码,码元速率为2Kb/S,码型为111100010011010,可对比TP001的2KHz的时钟信号读出它的码型序列。该波形用来输岀到FSK调制模块单元,作为FSK调制的数字基带信号(默认2KHz PN),也可通过薄膜键盘选择2KHz方波。

本实验平台中CPLD可编程器件EPM7128芯片产生的信号还有很多,学生可在以后实验过程中逐步遇到。

图1-2 CPLD可编程模块产生的部分信号波形示意图

五、实验报告要求

1.分析各种时钟信号及数字信号产生的方法,叙述其功用。

2.画出各种时钟信号及数字信号的波形

3.了解CPLD可编程技术方面的知识。