1.еЦЮеVCOбЙПиеёЕДЦїЕФЛљБОЙЄзїдРэ, МгЩюЖдЛљБОЫјЯрЛЗЙЄзїдРэЕФРэНтЁЃ

2.ЪьЯЄЫјЯрЪНЪ§зжЦЕТЪКЯГЩЦїЕФЕчТЗзщГЩгыЙЄзїдРэЁЃ

ЖўЁЂЪЕбщЕчТЗЙЄзїдРэ

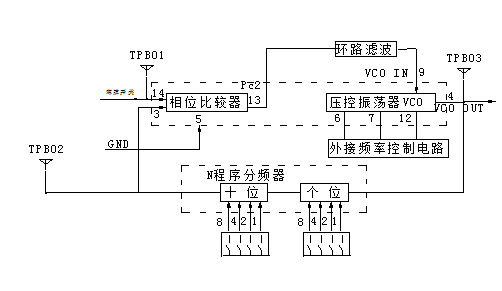

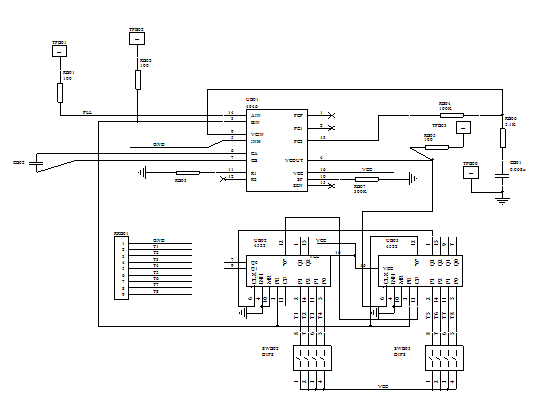

БОЕЅдЊПЩзіЛљБОЫјЯрЛЗКЭЫјЯрЪНЪ§зжЦЕТЪКЯГЩЦїСНИіЪЕбщЁЃзмЬхПђЭМШчЭМ8-1,ЕчТЗдРэЭМШчЭМ8-2ЫљЪОЁЃ

ЭМ8-1 ЛљБОЫјЯрЛЗгыЫјЯрЪНЪ§зжЦЕТЪКЯГЩЦїЕчдРэПђЭМ

ЭМ8-2 VCOЕчТЗЕчдРэЭМ

1.4046ЫјЯрЛЗаОЦЌНщЩмЃЈТдЃЉ

ЯъМћЫљИНЙтХЬ4046аОЦЌ

2.VCOбЙПиеёЕДЦї

ЫљЮНбЙПиеёЕДЦїОЭЪЧеёЕДЦЕТЪЪмЪфШыЕчбЙПижЦЕФеёЕДЦїЁЃ

4046ЫјЯрЛЗЕФVCOЪЧвЛИіЯпадЖШКмИпЕФЖраГеёЕДЦїЃЌЫќФмВњЩњКмКУЕФЖдГЦЗНВЈЪфГіЁЃЕчдДЕчбЙПЩЙЄзїдк3VЁЋ18VжЎМфЁЃБОЕчТЗШЁ+5VЕчдДЁЃЫќРћгУгЩУХЕчТЗзщГЩЕФRSДЅЗЂЦїПижЦвЛЖдПЊЙиЙмТжЗЌЕиЯђЖЈЪБЕчШнC1 е§ЯђГфЕчКЭЗДЯђГфЕчЃЌДгЖјаЮГЩздМЄеёЕДЃЌеёЕДЦЕТЪгыГфЕчЕчСїГЩе§БШЁЃгыC1ЕФШнСПГЩЗДБШЃЌеёЕДЦЕТЪВЛНігыЖЈЪБЕчШнC1ЁЂЭтМгПижЦЕчбЙUiгаЙиЖјЧвЛЙгыЕчдДЕчбЙгаЙиЃЌгыЭтНгЕчзшR1ЁЂR2ЕФБШжЕвВгаЙиЁЃ

3.ЫјЯрЪНЪ§зжЦЕТЪКЯГЩЦїЙЄзїдРэ

ДгЭМ8-2ПЩМћЃЌUB02(MC14522)ЁЂUB03(MC14522)ЮЊЖўМЖПЩдЄжУЗжЦЕЦїЃЌШЋВПВЩгУПЩдЄжУBCDТыЭЌВН1/NМЦЪ§ЦїMC14522ЃЌПЩгЩ4ЮЛаЁаЭВІЖЏПЊЙибЁдёЁЃUB02ЁЂUB03ЗжБ№ЖдгІзХзмЦЕБШNЕФЪЎЮЛЁЂИіЮЛЗжЦЕЦїЃЌUB02ЁЂUB03ЕФЪфШыЖЫвЛЗНУцSWB02ЁЂSWB03ЗжБ№жУШыЗжЦЕБШЕФЪЎЮЛЪ§ЁЂИіЮЛЪ§вд8421 BCDТыаЮЪНЪфШыЃЈЕЋ1010ЁЋ1111Ъ§жЕЛЙЪЧЦ№зїгУЕФЃЌгааЫШЄЕФЭЌбЇПЩгУвЛаЉгыУХЁЂЗЧУХЩшМЦвЛИіМђЕЅЕФдМЪјЕчТЗЃЌЪЙетаЉЗЖЮЇШЁжЕвЛТдЮЊ0000ЃЉЁЃ

ЪЙгУЪБАДЫљашЗжЦЕБШNдЄжУКУSWB02ЁЂSWB03ЕФЪфШыЪ§ОнЃЌf0 = N•fRЃЌ3ЮЛГЬађЗжЦЕЦїMC14522ЕФЪ§ОнЪфШыЖЫP0ЁЋP3ЗжБ№Нгга510KΩЕФЯТРЕчзшЃЌЕБSWB02ЁЂSWB03УЛгаЖдИУЯЕЭГЕЅдЊЪ§ОнЪфШыЪБЃЌМДПЊТЗзДЬЌЪБЃЌДЫЪБЯТРЕчзшАбЪ§ОнЪфШыЖЫжУ“0”ЕчЦНЃЛЕБSWB02ЁЂSWB03ЙЄзїЪБЃЌдђгаЯргІЕФ“1”ЕчЦНЪфШыЕНЪ§ОнЪфШыЖЫЃЌЪЙжЎжУгк“1”ЕчЦНзДЬЌЃЌвдБуГЬађЗжЦЕЦїНјааДІРэЁЃ?

дкЭМ8-2ЕчТЗЭМжаЃЌЕБГЬађЗжЦЕЦїЕФЗжЦЕБШNжУГЩ1ЃЌвВОЭЪЧАбSWB02ОљЖЯПЊЃЌSWB03жУГЩ“0001”зДЬЌЁЃетЪБЃЌИУЕчТЗОЭЪЧвЛИіЛљБОЫјЯрЛЗЕчТЗЁЃ

ЕБЖўМЖГЬађЗжЦЕЦїЕФNжЕПЩгЩЭтВПЪфШыНјааБрГЬПижЦЪБЃЌИУЕчТЗОЭЪЧвЛИіЫјЯрЪНЪ§зжЦЕТЪКЯГЩЦїЕчТЗЁЃЪфШыЦЕТЪгЩБЁФЄМќХЬНјаабЁдёЃЌ1KHZЛђ2KHZЗНВЈаХКХЃЌдђАбРДздЪЕбщвЛЕФЪБжгаХКХЗЂЩњЦї1KHzЛђ2KHZЗНВЈаХКХЪфШыЕНИУ14в§НХЁЃ

ЕБЫјЯрЛЗЫјЖЈКѓЃЌПЩЕУЕНЃК fRЃНfV

Цфжа fVЃНf0/N ,

ДњШыЕУЃК fR=f0/N

вЦЯюЕУЃК f0=N•fR

гЩДЫПЩжЊЃЌЕБfRЙЬЖЈВЛБфЪБЃЌИФБфЖўМЖГЬађЗжЦЕЦїЕФЗжЦЕБШNЃЌVCOЕФеёЕДЪфГіЦЕТЪ(вВОЭЪЧЦЕТЪКЯГЩЦїЕФЪфГіЦЕТЪ)f0вВЕУЕНЯргІЕФИФБфЁЃ

етбљЃЌжЛвЊЪфШывЛИіЙЬЖЈаХКХЦЕТЪfRЃЌМДПЩЕУЕНвЛЯЕСаЫљашвЊЕФЦЕТЪЃЌЦфЦЕТЪМфИєЕШгкfRЃЌетРяЮЊ1KHzЁЃбЁдёВЛЭЌЕФfRЃЌПЩвдЛёЕУВЛЭЌfRЕФЦЕТЪМфИєЁЃдкгУЪЕбщвЛаХКХЗЂЩњЦїВњЩњЕФЪБжгаХКХЦЕТЪЪБЃЌЦфзМШЗЦЕТЪЮЊ1.024KHzЃЌЖјВЛЪЧ1KHzЁЃвђЖјОЙ§ЖўМЖГЬађЗжЦЕЦїгыЫјЯрЪЕбщКѓЃЌVCOбЙПиеёЕДЦїЕФЪфГіЦЕТЪвВгІЕБЪЧ1.024KHzЕФNБЖЪ§ЁЃ

Ш§ЁЂЪЕбщФкШн

(вЛ)ЛљБОЫјЯрЛЗЪЕбщ

1.ЙлВьЫјЯрЛЗТЗЕФЭЌВНЙ§ГЬЃЛ

2.ЙлВьЫјЯрЛЗТЗЕФИњзйЙ§ГЬЃЛ

3.ЙлВьЫјЯрЛЗТЗЕФВЖзНЙ§ГЬЃЛ

4.ВтЪдЛЗТЗЕФЭЌВНДјгыВЖзНДјЃЌВЂМЦЫуЫќУЧЕФДјПэЁЃ

(Жў)ЫјЯрЪНЪ§зжЦЕТЪКЯГЩЦїЪЕбщ

1.дкГЬађЗжЦЕЦїЕФЗжЦЕБШNЃН1ЁЂ10ЁЂ100Ш§жжЧщПіЯТЃК

ЃЈ1ЃЉВтСПЪфШыВЮПМаХКХЕФВЈаЮЃЛ

ЃЈ2ЃЉВтСПЦЕТЪКЯГЩЦїЪфГіаХКХЕФВЈаЮЁЃ

2.ВтСПВЂЙлВьзюаЁЗжЦЕБШгызюДѓЗжЦЕБШЁЃ

ЫФЁЂЪЕбщВНжшМАзЂвтЪТЯю

ЃЈвЛЃЉЛљБОЫјЯрЛЗЪЕбщ

1.ЙлВьЛЗТЗЕФЭЌВНЙ§ГЬ

ЫјЯрЛЗдкЫјЖЈзДЬЌЯТЃЌШчЙћЪфШыаХКХВЮПМЦЕТЪfRБЃГжВЛБфЃЌЖјVCOЕФеёЕДЦЕТЪf0ЗЂЩњЦЎвЦЕМжТfV ≠ fRЪБЃЌдђдкЛЗТЗЕФЗДРЁПижЦзїгУЯТЃЌЪЙf0ЛжИДШдШЛБЃГжfv = fRЕФзДЬЌЃЌетжжЙ§ГЬНазіЭЌВНЙ§ГЬЁЃ

ЪЕбщЗНЗЈЃКНЋЭМ8-2ЕчТЗЭМжаSWB03ЩшжУЮЊ001зДЬЌЃЌДЫЪБЗжЦЕБШЮЊNЃН1ЁЃМДНЋГЬађЗжЦЕЦїЕФЗжЦЕБШЩшжУЮЊ1(дЄжУЮЊ001зДЬЌ)ЁЃЪЕбщЕчТЗЕФЫјЯрЛЗМДГЩЮЊЛљБОЫјЯрЛЗЁЃЦф

fV ЃН f0/N ЃН f0/1 ЃН f0

2.ЙлВьЛЗТЗЕФИњзйЙ§ГЬ

ЫјЯрЛЗНјШыЫјЖЈзДЬЌКѓЃЌШчЙћfV(ЯжЕШгкVCOЕФеёЕДЦЕТЪf0)ВЛБфЃЌЪфШыВЮПМЦЕТЪЗЂЩњЦЎвЦЃЌдђдкЛЗТЗЕФЗДРЁПижЦзїгУЯТЃЌЪЙf0ИњЫцзХfRЕФБфЛЏЖјБфЛЏЃЌвдБЃГжfV=fRЕФЛЗТЗЫјЖЈзДЬЌЁЃетжжЙ§ГЬНазіИњзйЙ§ГЬЁЃ

ЪЕбщЗНЗЈЃКдкЩЯУцЪЕбщЕФЛљДЁЩЯНЋЭтМгаХКХдДЕФЦЕТЪ(ВЮПМЦЕТЪfR)ж№ДЮИФБф(ФЃФтfRВњЩњЕФЦЎвЦ)ЃЌУПИФБфвЛДЮfRЃЌЙлВьвЛДЮfVЕФЪ§жЕЃЌПЩвдПДЕНЃЌfVИњзйfRЕФБфЛЏfV=fRЕФзДЬЌЁЃ

3.ЙлВьЛЗТЗЕФВЖзНЙ§ГЬ

ЫјЯрЛЗдкГѕЪМЪЇЫјзДЬЌЯТЃЌЭЈЙ§ЛЗТЗЗДРЁПижЦзїгУЃЌЪЙVCOЕФеёЕДЦЕТЪf0ЕїећfV=fRЕФЫјЖЈзДЬЌЃЌетИіЙ§ГЬГЦЮЊВЖзНЙ§ГЬЁЃ

ЪЕбщЗНЗЈЃКЕчТЗСЌНгЭЌЧАЯюЃЌTPB02ДІНгЦЕТЪМЦЃЌВтСПfVЕФЪ§жЕЃЌЪЕбщПЊЪМЪБНЋаХКХдДЦЕТЪ(fR)дЖРыVCOЕФжааФеёЕДЦЕТЪ(ШчСюfRИпгк1.5MHzЛђдЖЕЭгк1KH)ЪЙЛЗТЗДІгкЪЇЫјзД

ЬЌЃЌМДfV≠fRЃЌШЛКѓНЋfRДгИпЖЫЛКТ§ЕиНЕЕЭ(ЛђДгЕЭЖЫЛКТ§ЕиЩ§Ип)ЃЌЕБНЕЕЭ(ЛђЩ§Ип)ЕНвЛЖЈЪ§жЕЃЌЦЕТЪМЦЯдЪОfVЕШгкfRЪБМДfRВЖзНЕНСЫfVЛЗТЗНјШыЫјЖЈзДЬЌЁЃ

4.ВтЪдЛЗТЗЕФЭЌВНДјгыВЖзНДј

ЪЕбщЗНЗЈЃКЕчТЗСЌНгЭЌЧАЯюЃЌСюаХКХдДЦЕТЪ(fR)ЕШгк50KHzЁЃетЪБЛЗТЗгІДІгкЫјЖЈзДЬЌ(fV = fR)ЁЃ?

(1)Т§Т§діМгаХКХдДЕФЦЕТЪЃЌжБжСЛЗТЗЪЇЫј(fV≠fR)ЁЃДЫЪБаХКХдДЕФЪфГіЦЕТЪОЭЪЧЭЌВНДјЕФзюИпЦЕТЪЁЃ

(2)Т§Т§МѕаЁаХКХдДЕФЦЕТЪЃЌжБжСЛЗТЗЫјЖЈЃЌДЫЪБаХКХдДЕФЪфГіЦЕТЪОЭЪЧВЖзНДјЕФзюИпЦЕТЪЁЃ

(3)МЬајТ§Т§МѕаЁаХКХдДЕФЦЕТЪЃЌжБжСЛЗТЗЪЇЫјЃЌДЫЪБаХКХдДЕФЪфГіЦЕТЪОЭЪЧЭЌВНДјЕФзюЕЭЦЕТЪЁЃ

(4)Т§Т§діМгаХКХдДЕФЦЕТЪЃЌжБжСЛЗТЗЫјЖЈЃЌДЫЪБаХКХдДЕФЪфГіЦЕТЪОЭЪЧВЖзНДјЕФзюЕЭЦЕТЪЁЃ

(Жў)ЫјЯрЪНЪ§зжЦЕТЪКЯГЩЦїЪЕбщ

НЋSWB03ЖМжУгк0ЮЛЃЌSWB02ДгжУШыЪЎНјжЦЪ§9ПЊЪМЃЌж№НЅМѕжУЪ§жЕЃЌЕБЪфГіЦЕТЪВЛЗћКЯf0=NfRЕФЙиЯЕЪБЃЌБэЪОfRвбВЛФмЫјЖЈVCOЕФЦЕТЪЁЃЦЕТЪКЯГЩЦївбВЛФме§ГЃЙЄзїЁЃдђФмТњзуf0=N•fRЙиЯЕЪНЕФзюаЁЕФЗжЦЕБШжЕЃЌМДЮЊИУКЯГЩЦїЕФзюаЁЗжЦЕБШЁЃ

ЭЌРэЃЌдіДѓNЕФЪ§жЕФмЙЛТњзуf=N•fRЙиЯЕЪНЕФзюДѓЕФЗжЦЕБШжЕЃЌМДЮЊИУКЯГЩЦїЕФзюДѓЗжЦЕБШЁЃБОКЯГЩЦїЗжЦЕБШЕФБъзМЗЖЮЇ1ЁЋ99ЁЃ

ЮхЁЂВтСПЕуЫЕУї

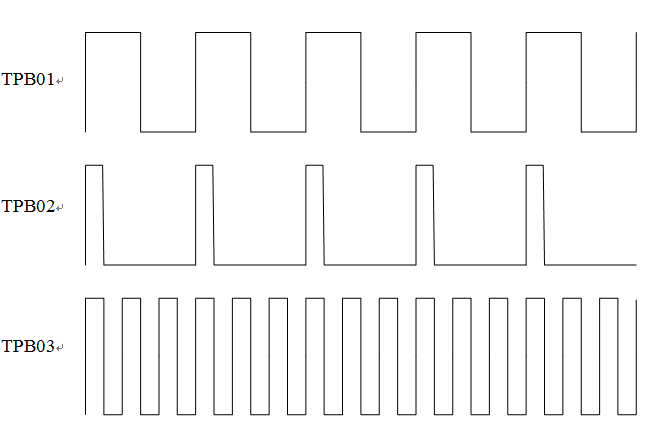

TPB01ЃКVCOЪфШыВЮПМаХКХЃЌМДЯрЮЛБШНЯЦїЪфШыаХКХЃЌЫќгЩБЁФЄМќХЬНјаабЁдёЃК

1KHZЛђ2KHZЛђЭтМгЪ§зжаХКХЃЈЭтМгаХКХНгS01“ЭтМгЪ§зжаХКХ”ЃЉЁЃ

TPB02ЃКЯрЮЛБШНЯЦїЪфШыаХКХЃЌЭЈГЃPDЮЊРДздVCOЕФВЮПМаХКХЁЃ

TPB03ЃКVCOбЙПиеёЕДЦїЕФЪфГіаХКХЁЃ

СљЁЂЪЕбщБЈИцвЊЧѓ

ЛГіЕчТЗПђЭММАЕчдРэЭМ,ИљОнЪЕбщФкШнЃЌЛГіЯргІЕФВЈаЮЃЌВЂзїЗжЮіЁЃ

ЭМ8-3 БЖЦЕN=3ЪБVCOВЈаЮЪОвтЭМ